3D封装的发展动态与前景

来源:本站 点击数:4614次 更新时间:2021/2/20 10:22:53

1 为何要开发3D封装

迄今为止,在IC芯片领域,SoC(系统级芯片)是最高级的芯片;在IC封装领域,SiP(系统级封装)是最高级的封装。 SiP涵盖SoC,SoC简化SiP。SiP有多种定义和解释,其中一说是多芯片堆栈的3D封装内系统集成(System-in-3D Package),在芯片的正方向上堆栈两片以上互连的裸芯片的封装,SIP是强调封装内包含了某种系统的功能。3D封装仅强调在芯片正方向上的多芯片堆栈,如今3D封装已从芯片堆栈发展占封装堆栈,扩大了3D封装的内涵。(1)手机是加速开发3D封装的主动力,手机已从低端(通话和收发短消息)向高端(可拍照、电视、广播、MP3、彩屏、和弦振声、蓝牙和游戏等)发展,并要求手机体积小,重量轻且功能多。为此,高端手机用芯片必须具有强大的存储器容量。2005年要求256Mb代码存储,1Gb资料存储;2006年要求1Gb代码存储,2Gb资料存储,于是诞生了芯片堆栈的封装(SDP),如多芯片封装(MCP)和堆栈芯片尺寸封装(SCSP)等;[1](2)在2D封装中需要大量长程互连,导致电路RC延迟的增加。为了提高信号传输速度,必须降低RC延迟。可用3D封装的短程垂直互连来替代2D封装的长程互连;(3)铜互连、低k介质层和CMP已成为当今CMOS技术中的一项标准工艺。随着芯片特征尺寸步入纳米尺度,对低k介质层要求越来越高,希望采用纯低k(k<2.8)介质层。然而事与愿违,ITRS曾三次(三个节点)延期向低k介质层的切换。2003年底在Sematech联盟主办的一次研讨会上,与会者认为,为改良IC互连面进行的低k材料研究有可能接近某种实际极限,未来应更多注重改进设计及制造低k介质层的能力,这表明实施SoC的难度。这就是开发3D封装的三条理由。从此,3D封装如雨后春笋般地蓬勃发展。

2 芯片堆栈

手机已成为高密度存储器最强、最快的增长动力,它正在取代PC成为高密度存储器的技术驱动,在2008年手机用存储器可能超过PC用存储器。用于高端手机的高密度存储器要求体积小、容量大,势必采取芯片堆栈。芯片堆栈的封装主要两种,一是MCP,二是SCSP。MCP涵盖SCSP,SCSP是MCP的延伸,SCSP的芯片尺寸比MCP有更严格的规定。通常MCP是多个存储器芯片的堆栈,而SCSP是多个存储器和逻辑器件芯片的堆栈。

2.1 芯片堆栈的优缺点

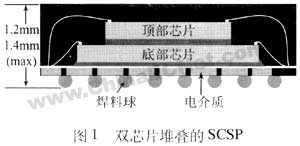

2004年3月Sematech预言,3D芯片堆栈技术将会填补现行的CMOS技术与新奇技术(如碳纳米管技术)之间的空白。芯片堆栈于1998年开始批量生产,绝大多数为双芯片堆栈,如图1所示。[2]到2004年底ST微电子已推出堆栈9个芯片的MCP,MCP最具经济效益的是4~5个芯片的堆栈。芯片堆栈的优缺点、前景和关系如表1所示,表1给出了芯片堆栈与封装堆栈的比较。[3]由于芯片堆栈在X和Y的2D方向上仍保持其原来的尺寸,并在Z方向上其高度控制在1mm左右,所以很受手机厂商的青睐。芯片堆栈的主要缺点是堆栈中的某个芯片失效,整个芯片堆栈就报废。

2.2 芯片堆栈的关键技术

芯片堆栈的关键技术之一是圆片的减薄技术,目前一般综合采用研磨、深反应离子刻蚀法(DRIE)和化学机械抛光法(CMP)等工艺,通常减薄到小于50μm,当今可减薄至10~15μm,为确保电路的性能和芯片的可靠性,业内人士认为晶圆减薄的极限为20μM左右,表2给出对圆片减薄的要求,即对圆片翘曲和不平整度(即粗糙度)提出的具体控制指标。

2.3 芯片堆栈的最新动态

至2005年2月底,芯片堆栈的最高水平是富士通和英代尔,富士通存储器芯片堆栈8个芯片,芯片厚度25μm,芯片尺寸为8mm×12mm,芯片堆栈封装高度小于2.0mm。英代尔存储器芯片堆栈6个芯片,芯片厚度50~75μm,芯片尺寸8mm×10mm/8mm×11mm,芯片堆栈封装高度小于1.0mm。2005年4月ST微电子也推出堆栈8个芯片的MCP,芯片厚度40μm,芯片间"中介层"厚度40μm,芯片堆栈封装高度为1.6mm,采用这种8个芯片堆栈的存储器,使过去1Gb存储器占用的电路板现在能容纳1GB的存储器。[4]ST微电子还推出超薄窄节距双芯片堆栈的UFBGA,封装高度仅0.8mm,采用BGA工艺处理只有正常圆片厚度的1/4,金丝球焊高度也降至40μm。该公司通常的MCP是堆栈2~4个不同的类型的存储器芯片,如SRAM,快闪存储器或DRAM。ST微电子于2004年推出4片堆栈的LFBGA,其高度为1.6mm,2005年将降至1.2mm,2006年再降至1.0mm。[5]MCP存储器在日本、韩国的手机、数码相机和便携式游戏机中被广泛采用。如三星电子向索尼便携式 Play Station游戏机提供容量64Mb的双片堆栈 MCP,它含256Mb NAND快闪存储器和256Mb DDR DRAM,还向索尼数码相机提供存储器MCP,它含移动DRAM+NOR快闪存储器,移动DRAM+one NAND快闪存储器,国外已推出用于3G手机的8个芯片堆栈的MCP,其尺寸为11mm×14mm×1.4mm,容量为3.2Gb,它含2片1Gb NAND快闪存储器,2片256Mb NOR快闪存储器、2片256Mb移动DRAM、1片128Mb Ut RAM和1片64Mb Ut RAM。参与芯片堆栈技术的公司还有Matrix、Tezzaron和IrVine Sensors等公司。至2004年底Matrix已交付100万块3D封装的一次性可编程非易失性存储器,采用0.15μm工艺和TSOP或Multi Media Card封装,密度达64MB。Tezzaron采用0.18μm工艺推出双片堆栈的3D封装。

2.4 芯片堆栈的互连[2]

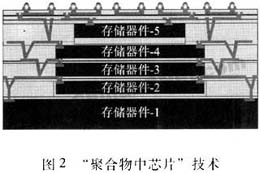

从图1可知,芯片间的互连是采用金丝球焊的方式来完成的,这要求金丝球形成高度必须小于75μm,当多个芯片堆栈时,对金丝球焊的要求更高,即要求金丝球焊的高度更低。IMEC、Fraunhofe-Berlin和富士通等公司联合推出"聚合物中芯片"工艺,它不采用金丝球焊,而采用硅垂直互连的直接芯片/圆片堆栈,将芯片减薄后嵌入到薄膜或聚合物基中,见图2。它的关键技术是:①通孔,采用DRIE(深反应离子刻蚀)制备硅孔,如采用SF6快速刻蚀硅,在多工艺部的各向异性刻蚀过程中可使用C4F8钝化通孔侧壁;②通孔填注,在300℃下用TEOS CVD淀积SiO2绝缘层,然后淀积TiN/Cu或TaN/Cu;③圆片与圆片或芯片与圆片之间精确对准,目前最好的对准精度为±1~2μm,它限制了该技术的广泛应用;④圆片与圆片键合,可采用硅熔法、聚合物键合法、直接Cu-Cu法或Cu-Sn共晶键合法等。圆片与圆片堆栈技术适用于多芯片数的圆片;芯片与圆片堆栈技术适用于少芯片数的圆片,它要求先选出KGD,然后将KGD粘合到基板圆片上。

3 封装堆栈[3]

尽管芯片堆栈封装在超薄的空间内集成了更多的功能,甚至某个系统功能,但是在一些IC内由于良品率的影响和缺乏KGD,使封装IC必须进行3D配制下的预测试。为此,业界推出了在单一解决方案内堆栈预测试的封装,即封装堆栈,它可作为无线应用(如手机、PDA等)的一个备选方案。封装堆栈的优缺点及前景如表1所示。封装堆栈又称封装内的封装堆栈,它有两种形式(见图3)。一是PiP(Package-in-Package Stacking),PiP是一种在BAP(Basic Assembly Package,基础装配封装)上部堆栈经过完全测试的内部堆栈模块(ISM,Inside Stacked Module),以形成单CSP解决方案的3D封装。二是PoP (Pockage-on-Package Stacking),他是一种板安装过程中的3D封装,在其内部,经过完整测试的封装如单芯片FBGA(窄节距网格焊球阵列)或堆栈芯片FBGA被堆栈到另外一片单芯片FBGA(典型的存储器芯片)或堆栈芯片FBGA(典型的基带或模拟芯片)的上部,这样封装堆栈能堆栈来自不同供应商的混合集成电路技术的芯片,允许在堆栈之前进行预烧和检测。

目前美国Amkor、新加坡STATS Chip PAC等IC封装和测试厂商都能量产封装堆栈。如今CSP的封装堆栈已研发出多种不同形式,如图4所示。当前PCB板和封装转接板的布线限制规定为0.5mm或0.4mm,它是CSP封装的最小实用间距,所以CSP封装的焊球间距目前流行的是0.65mm和0.5mm。在封装堆栈中需采用回流焊工艺,一般底部封装模盖的厚度必须小于顶部堆栈封装焊接球支架的高度,为了获得尽可能大的支架高度,选择CSP焊球间距的65%为实际焊球的直径,见表3。在回流焊中,当焊剂掩模开口尺寸是CSP焊球间距的1/2时,支架高度经封装堆栈后的高度如表3最后一排所示。

网友点评

参与点评